Rangkaian flip-flop merupakan suatu rangkaian yang terdiri dari dua elemen aktif yang bekerja secara bergantian. Rangkaian ini berfungsi sebagai pencacah pulsa, menyimpan bilangan biner, dan mensinkronisasikan suatu rangkaianaritmatika. Rangkaian inibersifat bistable (dua kondisi yang stabil 0 dan1 ) dan akan tetap stabil jika tidak ada inputan yangmasuk. Oleh karena itu tidak ada table kebenaran yang pasti untuk tiap rangkaian, karena tiap kali diberikan inputan 0-0,maka hasilnya akan direset dan mengeluarkan output yang berbeda jika kita beri inputan yang sama sebelum direset. Bila inputan diberi nilai 1-1,maka output yang dihasilkan akan mengeluarkan nilai yang ada sebelumnya. Inputan iniberfungsi sebagi penyimpan nilai yang sebelumnya.

Rangkaian flip-flop ada beberapa jenis, diantaranya :

1. 1RS FLIP-FLOP

2. JK FLIP-FLOP

3. JK FLIP-FLOP dengan Preset dan Clear

4. D FLIP-FLOP

5. MASTER-SLAVE FLIP-FLOP

Praktikum pertama membahas tentang RS FLIP-FLOP dari gerbang NAND menggunakan IC 7400.

skema RS Flip-Flop dengan NAND Gate:

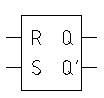

Simbol RS Flip-Flop :

Tabel Kebenarannya:

Praktikum kedua membahas tentang RS FLIP-FLOP dari gerbang NOR menggunakan IC 7402.

skema RS Flip-Flop dengan NOR Gate:

Praktikum ketiga membahas tentang RS FLIP-FLOP dari dua gerbang NAND menggunakan IC 7400 dan menggunakan Clock.

skema RS Flip-flop dengan NAND Gate dan Clock:

Rangkaiannya adalah:

Praktikum keempat membahas tentang RS FLIP-FLOP dengan Clock dari gerbang NAND dan NOR menggunakan IC 7400 dan IC 7402.

Penjelasan tentang jenis FLIP-FLOP lainnya:

a. JK FLIP-FLOP

PFF JK mempunyai masukan "J" dan "K". FF ini "dipicu" oleh suatu pinggiran pulsa clock positif atau negatif. FF JK merupakan rangkaian dasar untuk menyusun sebuah pencacah. JK FLIP-FLOP pada dasarnya terbentuk dari RS FLIP-FLOP yang telah dimodifikasi dengan penambahan gerbang AND pada sisi input RS-nya. Cara kerja flip-flop ini adalah:

1) Pada saat J dan K keduanya rendah, gerbang AND tidak merespon sehingga output Q tetap bertahan pada keadaan terakhirnya.

2) Saat J rendah dan K tinggi, FF akan direset hingga output yang diperoleh Q = 0. Terkecuali jika FF memang sudah dalam keadaan set atau Q sudah dalam keadaan tinggi.

3) Saat J tinggi dan K rendah, maka inputan akan mereset FF hingga diperoleh output Q = 1 dengan kondisi yang sama dengan keadaan sebaliknya.

4) Saat keduanya tinggi, FF ada pada keadaan toggle yang berarti output Q akan berpindah pada keadaan lawan jika pinggiran pulsa clocknya tiba.

Gambar JK FLIP-FLOP

b. D FLIP-FLOP

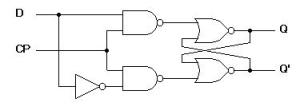

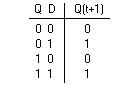

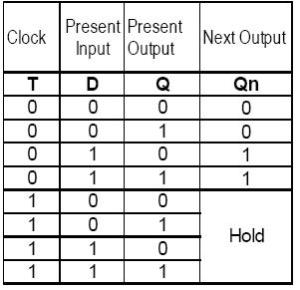

D flip-flop adalah RS flip-flop yang ditambah dengan suatu inventer pada reset inputnya. Sifat dari D flip-flop adalah bila input D (Data) dan pulsa clock berlogik 1, maka output Q akan berlogik 1 dan bilamana input D berlogik 0, maka D flip-flop akan berada pada keadaan reset atau output Q berlogik 0.

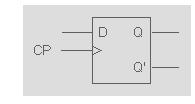

Symbolnya :

Logic diagram dengan nand nya:

Transisi table

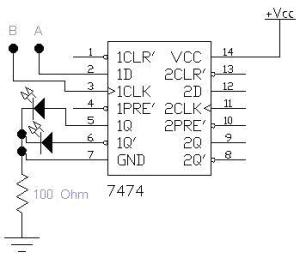

IC yang dipakai adalah IC 7474

Skema ic ya:

Model operasinya

c. MASTER-SLAVE FLIP-FLOP

Sebuah Master-Slave JK-FF dibentuk dari dua buah SR-FF, dimana operasi dari kedua SR-FF tersebut dilakukan secara bergantian, dengan memberikan input Clock yang berlawanan pada kedua SR-FF tersebut. Prinsip dasar dari Master-Slave JK-FF adalah sebagai berikut : jika Clock diberi input “1”, gerbang AND 1 dan 2 akan aktif, SR-FF ke-1 (Master) akan menerima data yang dimasukkan melalui input J dan K, sementara gerbang AND 3 dan 4 tidak aktif (menghasilkan output = “0”), sehingga SR-FF ke-2 (Slave) tidak ada respons (kondisinya sama dengan kondisi sebelumnya). Sebaliknya jika Clock diberi input “0”, gerbang 3 4 aktif, Slave akan mengeluarkan output di Q dan Q’, sementara Master tidak me-respons input, karena gerbang AND 1 dan 2 tidak aktif.

Kita dapat membangun suatu flip-flop JK dari gerbang NAND. Nampak bahwa sebenarnya flip-flop JK terdiri dari dua flip-flop yang terangkai menjadisatu. Flip-flop yang kedua (slave-budak) mengikuti keadaan yang ditentukan oleh flipflop yang pertama (master-tuan). Suatu transisi hanya dapat terjadi dengan satu pulsa clock penuh. Kejadian dibawah ini terjadi selama urutan pemacuan pulsa pada titik-titik bernomor.

1. Master dan Slave diisolasikan/dipisahkan.

2. Data dimasukkan dari input J dan K, berhenti di Master.

3. Input J dan K Master ditutup.

4. Slave mengambil data dari output Master.

skema Master Slave:

implementasi dengan IC 7476:

tabel Model Operasi:

Komentar ini telah dihapus oleh pengarang.

BalasHapus